Dual J-K Flip-Flops

Description

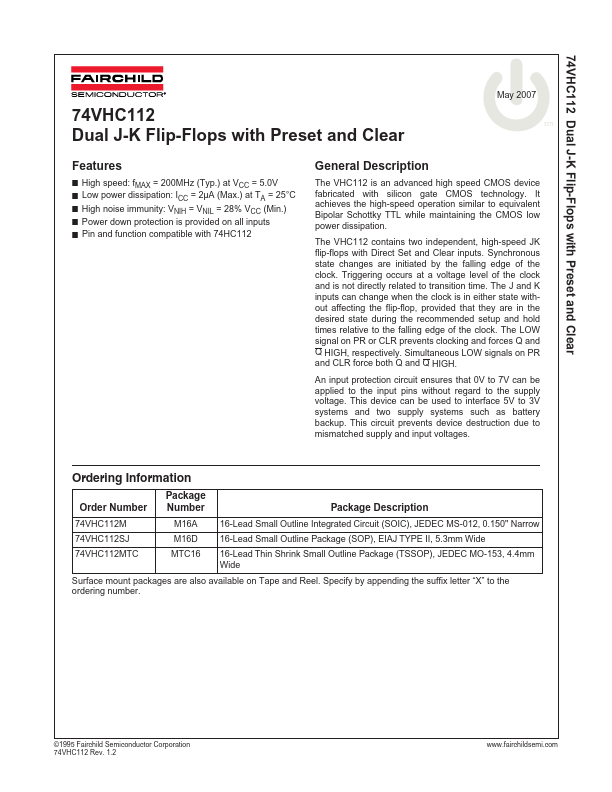

74VHC112 Dual J-K Flip-Flops with Preset and Clear

74VHC112 Dual J-K Flip-Flops with Preset and Clear

May 2007

tm

Features

■ High speed: fMAX = 200MHz (Typ.) at VCC = 5.0V ■ Low power dissipation: ICC = 2µA (Max.) at TA = 25°C ■ High noise immunity: VNIH = VNIL = 28% VCC (Min.) ■ Power down protection is provided on all inputs ■ Pin and function compatibl...

Fairchild Semiconductor

74VHC112

74VHC112 PDF File

Similar Datasheet